yeonseong

stored program computer개념을 제시한 폰 노이만 컴퓨터 구조의 특징과 문제점 본문

폰 노이만 컴퓨터 구조: 개념과 저장 프로그램(Stored-Program)

폰 노이만 아키텍처는 프로그램과 데이터를 동일한 메모리에 저장하고 공용 버스로 접근하는 저장 프로그램 구조를 제안한 모델이다. 즉, 주기억장치에 명령어와 데이터가 함께 저장되며 중앙처리장치(CPU)는 제어장치(CU)와 산술논리연산장치(ALU), 레지스터 등을 이용해 메모리로부터 명령을 인출(fetch), 해독(decoding), 실행(execution)하는 순차적 처리 방식을 따른다. 이 구조에서는 CPU, 메모리, 입출력 장치가 버스로 연결되며, 저장된 프로그램 개념에 따라 명령어와 데이터를 동일한 매체에서 처리할 수 있는 유연성을 확보했다.

본론

1) 폰 노이만 구조 개요 및 Stored-Program 개념

폰 노이만 구조는 1945년 폰 노이만이 발표한 EDVAC 보고서에서 구체화된 컴퓨터 구조로, 이후 대부분 현대 컴퓨터의 기반이 되었다. 저장 프로그램 구조란 명령어를 메모리에 저장하여 프로그램을 수행하는 방식으로, 초기 천공 카드나 플러그보드 대신 메모리 내 저장 프로그램을 이용해 프로세서를 유연하게 재구성한다. 이로써 한 시스템으로 다양한 연산 프로그램을 실행할 수 있게 되었고, 계산기나 고정된 하드와이어 회로와는 달리 범용 컴퓨팅이 가능해졌다.

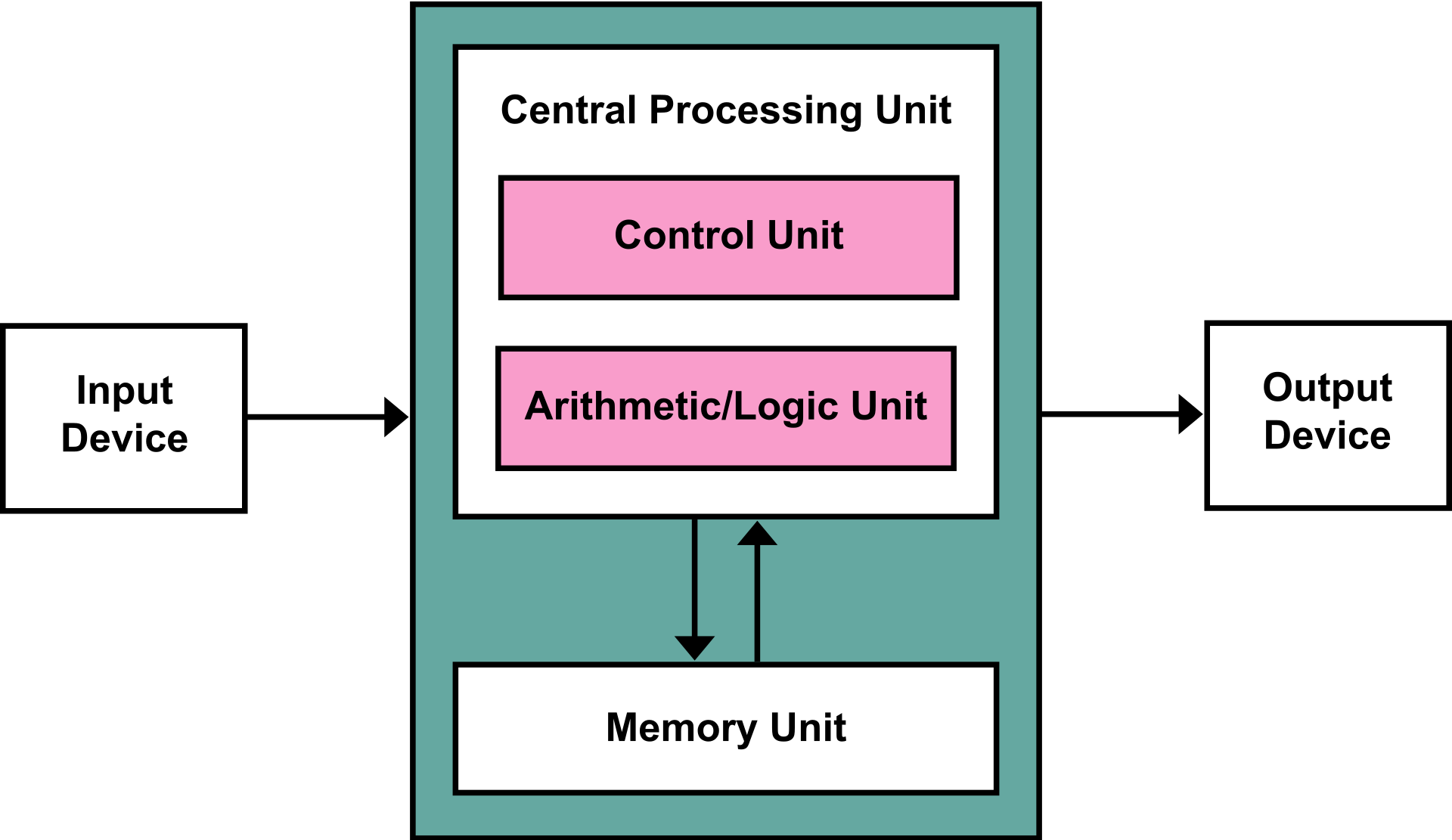

구성 요소: 폰 노이만 구조의 주요 구성 요소는 중앙처리장치(CPU: 산술논리연산장치(ALU)와 제어장치(CU) 포함), 주기억장치(Main Memory), 입력장치(Input), 출력장치(Output)이다. CPU 내 제어장치는 프로그램 카운터와 명령 레지스터를 포함하여 다음 실행될 명령의 주소를 관리하고, ALU는 실제 연산·비교 연산을 수행한다. 주기억장치는 주소에 따라 명령어와 데이터를 저장하며, 입출력 장치는 외부 장치와 정보를 교환한다. 이들 간의 통신은 단일 주소 버스와 데이터 버스로 이루어지는데, 예를 들어 그림 1과 같이 CPU와 메모리가 버스로 연결된다.

그림 1. 폰 노이만 구조의 기본 구성도 (입력, CPU(ALU·제어장치), 메모리, 출력)

2) 구조적 특징 및 장점

폰 노이만 구조의 구조적 특징으로는 명령어와 데이터가 동일 메모리에 저장되고 단일 버스를 공유한다는 점이 가장 두드러진다. 이로 인해 설계가 단순해지고 하드웨어 구성이 간결해진다. 예를 들어 주기억장치 단일 체계로 두므로 회로 복잡성이 줄어들고, 멀티플렉서나 별도 메모리 없이도 다양한 프로그램이 실행 가능하므로 범용 컴퓨터 설계에 적합하다. 이로 인해 비용 효율성이 높고 시스템 확장 및 업그레이드가 비교적 용이하다는 장점이 있다. 실제로 단일 메모리 구조 덕분에 CPU가 내부 버퍼 없이도 모든 명령어·데이터를 취급할 수 있어 하드웨어 복잡도와 비용이 절감된다.

장점: 폰 노이만 구조의 대표적 장점은 다음과 같다.

첫째, 단순한 설계: 데이터와 명령어를 동일한 메모리에 저장하여 하드웨어 구성이 간소하다.

둘째, 비용 효율성: 메모리와 버스 자원을 공유하므로 부품 수가 적고 제조 비용을 줄일 수 있다.

셋째, 유연성: 다양한 프로그램을 동일한 시스템에서 구동할 수 있어 범용적이고 확장 가능하다. 이러한 특성 덕분에 폰 노이만 구조는 소형 임베디드 시스템부터 대형 서버에 이르기까지 광범위하게 적용된다.

3) 구조적 문제점 및 병목 현상

그러나 폰 노이만 구조에는 근본적인 성능 한계가 존재한다. **폰 노이만 병목(Von Neumann Bottleneck)**으로 알려진 문제는 명령어와 데이터가 단일 버스로 오가면서 발생한다. 즉, 한 번에 하나의 데이터 전송만 가능하기 때문에 명령어 인출(fetch)과 데이터 읽기/쓰기(read/write)가 동시에 일어날 수 없어 데이터 흐름이 제한된다. 예를 들어 CPU가 1초에 1만 개의 명령을 처리할 수 있어도, 메모리 인터페이스가 1초에 1000개만 공급한다면 CPU는 대부분의 시간을 메모리 응답을 기다리며 유휴 상태가 된다. 이러한 산술장치와 메모리 사이의 속도 불균형은 성능 개선의 큰 장벽이 된다.

메모리 벽(Memory Wall): CPU 성능은 지속적으로 발전해 왔지만 메모리 대역폭은 상대적으로 느리게 증가하여 메모리 벽 문제가 심화되었다. 메모리 속도가 프로세서 연산 속도에 비해 크게 느리기 때문에, 프로세서는 작업 대부분을 메모리에서 데이터를 기다리며 보내게 된다. 이로 인해 CPU가 데이터를 얻기 전까지 대기 시간이 길어지고, 전체 시스템 처리량이 제한된다. 예를 들어 20년간 CPU 연산능력은 수만 배 증가했지만 DRAM 대역폭은 수십 배에 그친다는 보고도 있다. 결국 폰 노이만 구조에서는 CPU와 메모리 간 데이터 전송 속도가 시스템 처리속도를 결정짓는 병목으로 작용한다.

4) 문제점 해결을 위한 기술적 접근

폰 노이만 병목을 완화하기 위해 여러 기술이 고안되었다. 대표적인 해결책은 하버드(Harvard) 구조로, 명령어와 데이터를 분리된 메모리와 버스로 처리하는 방식이다. 그림 2에서 보듯 하버드 구조는 명령 메모리와 데이터 메모리를 별도로 두어 CPU가 명령어를 인출하는 동안 동시에 데이터를 읽고 쓸 수 있다. 이를 통해 버스 충돌을 방지하고 명령 및 데이터 접근을 병렬화할 수 있어 처리속도를 크게 향상시킨다. 즉, 하버드 구조는 폰 노이만 구조보다 복잡하지만, 고속 데이터 처리가 필요한 임베디드 시스템이나 신호처리 응용에 유리하다.

그림 2. 하버드 아키텍처의 개념도 (명령 메모리와 데이터 메모리 분리)

캐시 메모리(Cache): 메모리 계층 구조에서 캐시는 CPU 내부에 고속의 SRAM 메모리를 두어 최근 사용 데이터와 명령을 저장한다. 캐시를 도입하면 CPU가 반복적으로 접근하는 데이터를 캐시에서 제공하므로 주기억장치 접근 빈도를 줄이고 버스 대역폭 한계를 완화할 수 있다. 예를 들어 L1L3 캐시 계층을 통해 주기억장치 대비 수십수백 배 빠른 접근이 가능해져 병목 현상을 상당 부분 경감한다.

파이프라이닝 및 병렬처리: 명령어를 단계별로 병렬 처리하는 파이프라이닝, 멀티코어·다중 스레드 등 병렬 아키텍처도 성능 한계를 극복한다. 파이프라인을 통해 여러 명령어를 동시에 처리하고, 멀티코어 CPU는 다중 워크로드를 병렬 처리해 연산량을 증대시킨다. 또한 벡터 연산 유닛, GPU·NPU 등 특수 가속기도 도입되어 동일한 명령어를 다수의 데이터에 병렬 수행함으로써 처리량을 극대화한다.

메모리·인터커넥트 개선: 고대역폭 메모리(HBM), 캐시 일관성 프로토콜 개선, CXL 등 고속 인터커넥트 기술이 발전함에 따라 메모리 접근 병목이 완화되고 있다. 예를 들어 CPU와 GPU/FPGA 사이를 직접 연결하는 NVLink나 AMD의 Infinity Fabric과 같은 버스 구조, PCIe 5.0/6.0 및 CXL 메모리 확장 기술은 대역폭을 크게 높여 폰 노이만 병목을 완화한다. 또한 **PIM(Processing-In-Memory)**과 같은 메모리 내 연산 기술도 연구되어, 연산 유닛을 메모리 칩 내부나 인접 공간에 배치하여 메모리-계산 병목을 근본적으로 해소하려는 시도가 이루어지고 있다.

5) 유사/대체 구조와의 비교 분석

폰 노이만 구조와 대표적 대안인 하버드 구조를 비교하면 다음과 같다. 명령어와 데이터를 공유 메모리에 저장하는 폰 노이만 구조는 설계가 간단하고 범용성이 높으나, 동일 버스 공유로 인한 병목이 단점이다. 반면 하버드 구조는 명령어 메모리와 데이터 메모리가 분리되어 동시 접근이 가능해 속도가 빠르지만, 메모리 체계가 이중화되어 설계가 복잡하고 비용이 높아지는 단점이 있다.

구조 메모리 저장 방식 장점 단점

| 폰 노이만 | 명령어+데이터 단일 메모리 | 설계 단순·유연성 높음 | 단일 버스 병목 |

|---|---|---|---|

| 하버드 | 명령어/데이터 별도 메모리 | 명령·데이터 병렬 접근 가능 | 설계 복잡·유연성 저하 |

실제 설계에서는 두 방식을 혼합한 변형 하버드 구조(명령/데이터 캐시 분리)도 널리 사용된다. 예를 들어 현대 x86 CPU는 하버드 스타일로 L1 명령 캐시와 데이터 캐시를 분리하여 어느 정도 동시 접근을 허용하는 한편, 실질적 주기억장치는 단일 공간을 사용하는 폰 노이만 구조의 특징을 유지한다.

6) 최신 기술 동향

최근 컴퓨터 아키텍처 분야에서는 인공지능, 빅데이터 시대의 요구를 반영한 다양한 최신 기술이 도입되고 있다. 먼저 AI 가속기 분야에서는 GPU·TPU·NPU와 같은 도메인 특화 프로세서가 폰 노이만 구조의 한계를 극복한다. 예를 들어 IBM 연구진은 AI 연산 전용 장치를 개발하며 폰 노이만 병목을 타파하려고 노력 중이다. 또한 메모리 벽을 직접적으로 해결하기 위해 PIM 기술이 활발히 연구되며, SK하이닉스·삼성전자 등에서 PIM 기반 메모리 칩을 선보이고 있다.

RISC-V와 SoC: RISC-V 같은 오픈소스 명령어 집합 아키텍처(ISA)의 부상으로 설계 유연성이 높아지고 있다. RISC-V는 라이선스 비용 부담 없이 커스터마이즈가 가능하며, 벡터 확장이나 도메인별 가속 기능을 손쉽게 추가할 수 있어 AI 가속기 및 IoT 칩 설계에 주목받고 있다. 실제로 국내 기업도 RISC-V 기반 AI 가속 칩을 개발하고 있고, SiFive·Tenstorrent 등에서 RISC-V를 기반으로 대규모 AI 연산을 지원하는 제품을 출시했다. SoC(System-on-Chip) 설계 트렌드 역시 지속되는데, CPU·GPU·AI엔진·메모리 컨트롤러 등을 하나의 칩에 집적하여 데이터 이동 거리를 줄이고 시스템 효율을 높인다. 칩렛(Chiplet) 방식과 NoC(Network-on-Chip) 기술도 발전하여 다중 칩 간 고속 인터커넥트를 제공한다.

이외에도 RISC-V 커뮤니티의 활발한 사양 확장과 더불어 메모리 기술의 진화(DDR5, LPDDR5X, CXL 메모리 등)가 진행 중이며, 양자 컴퓨팅·뉴로모픽 컴퓨팅과 같은 새로운 계산 패러다임도 연구되어 차세대 컴퓨팅 아키텍처 발전을 예고하고 있다.

결론

폰 노이만 컴퓨터 구조는 저장 프로그램 개념을 구현하여 현대 디지털 컴퓨팅의 근간을 이루었으나, 단일 메모리 공유로 인한 병목 문제를 내포한다. 이를 해결하기 위해 하버드 구조, 캐시 메모리, 파이프라이닝, 병렬 처리 등 다양한 기술이 도입되었으며, 최근에는 AI 가속기와 메모리 기술 혁신이 새로운 전기를 마련하고 있다. 실무적으로는 애플리케이션 특성에 맞는 아키텍처 선택이 중요하다. 예를 들어 실시간 임베디드 시스템이나 DSP 분야에서는 명령/데이터 분리 방식을, 범용 서버나 PC에서는 확장성 높은 폰 노이만 혼합 구조를 사용할 수 있다. 향후 기술 발전 방향으로는 메모리-계산 융합(PIM), HBM/저전력 DRAM, CXL 같은 고속 메모리 인터커넥트와 더불어 RISC-V 기반의 맞춤형 설계가 강조될 것이다. 결론적으로, 폰 노이만 아키텍처의 강점을 유지하면서 병목을 줄이는 방향으로 다양한 아키텍처 및 하드웨어 최적화가 계속해서 필요하며, 이러한 기술 동향을 면밀히 검토하고 반영하는 것이 중요하다.

REF

신뢰할 만한 참고자료 링크 정리

1. 원문 및 역사적 문서

- First Draft of a Report on the EDVAC (PDF) - MIT

폰노이만이 작성한 EDVAC 보고서 초안 원문. - First Draft of a Report on the EDVAC - Wikipedia

보고서의 기술적 내용과 논쟁적 배경 분석. - EDVAC - Wikipedia

EDVAC의 개발 과정 및 기술적 특성 설명.

2. 표준 교재 및 학술 서적

- Computer Architecture (Hennessy & Patterson) - Blackwell's

현대 컴퓨터 아키텍처 이론을 다룬 권위 있는 교재. - Structured Computer Organization (Tanenbaum) - Goodreads

컴퓨터 시스템의 계층적 구조를 설명하는 대학 교재.

3. 학술 논문 및 기술 보고서

- Can Programming Be Liberated from the von Neumann Style? (Backus, 1977)

튜링상 수상 연설문. 폰노이만 구조의 프로그래밍 한계 비판. - Atomic Layer-Deposited HfAlOx-Based RRAM (NCBI)

폰노이만 병목 현상을 극복하기 위한 메모리 내 처리 기술 연구. - On the Original Copies of "First Draft..." (Academia.edu)

보고서 사본의 변형 과정 및 역사적 영향 분석.

4. 온라인 참고 자료

- Von Neumann Architecture - Wikipedia

구조적 특징과 병목 현상에 대한 체계적 설명. - Stored-Program Computer - Wikipedia

하버드 아키텍처와의 비교 포함.

5. 기술 표준 및 아키텍처 발전

- The Origins, Uses, and Fate of the EDVAC (PDF)

EDVAC의 설계 배경 및 기술적 발전 과정. - First Draft of a Report on the EDVAC (SciSpace PDF)

보고서의 논리적 설계 개념과 생물학적 유사성 분석.

6. 기타 관련 자료

- UNIX 파이프 구현 소스 코드 (Semantic Scholar)

초기 컴퓨팅 시스템의 소프트웨어 설계 사례. - Can Programming Be Liberated... (ACM Digital Library)

Backus의 논문 공식 버전.

'정보관리기술사' 카테고리의 다른 글

| CISC와 RISC의 명령어 구조 비교 심화 분석 (1) | 2025.05.21 |

|---|---|

| CPU 중앙처리장치 (1) | 2025.05.15 |

| 컴퓨터 시스템의 하드웨어, 소프트웨어, 펌웨어의 구성요소와 발전방향 (0) | 2025.05.14 |

| 컴퓨터 5대 구성요소 (0) | 2025.05.10 |

| 정보관리기술사 준비를 시작하며 (0) | 2025.05.09 |